A device that increases computational processing power in a single Gate All-Around Field Effect Transistor including quantum-based features.

A major problem with conventional transistor technology is that conventional MOSFETs are ill equipped to implement multivalued logic. As the number of states a transistor can store increases, the number of transistors required on a chip decrease. Thus, with binary transistors, more transistors are needed to carry out a given number of logic functions. A related problem with conventional transistor technology is that as transistor size continues to shrink, charge leakage becomes more prominent and noise margin becomes less uniform. In non-volatile memory charge leakage will, over time, result in destruction of the information stored in a memory cell.

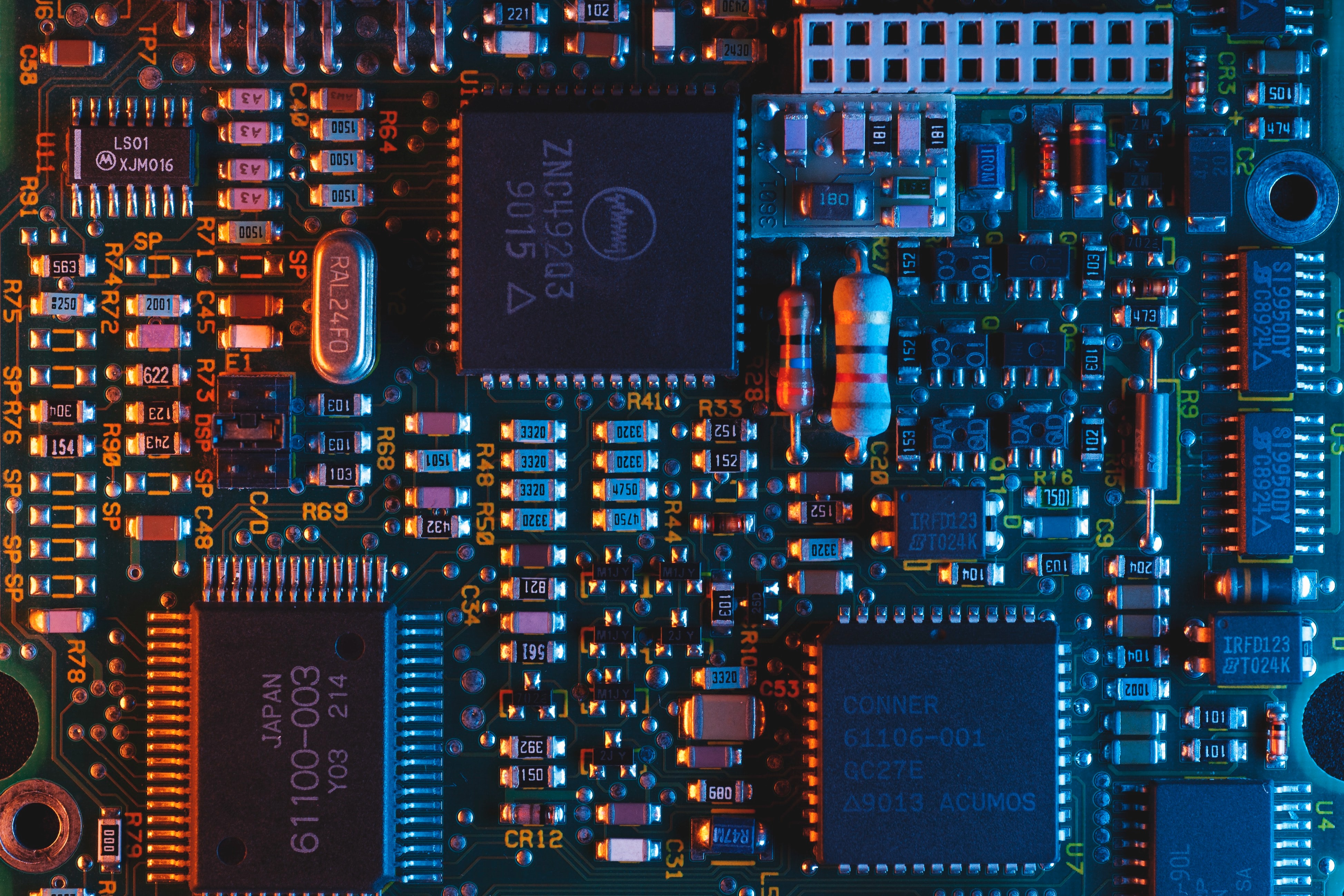

The device developed by SUNY Farmingdale State College researchers contains Circular Multi-channel (e.g., three-state, four-state) Gate All-Around Field Effect Transistors (GAAFET) which utilize quantum-based features or layers therein to increase computational processing during operation. Examples, of the quantum-based features included in the GAAFET include a plurality of quantum dots (QD) or quantum well channels. The quantum-based features are arranged in the GAAFET in a circumferential layer(s) that surrounds a nanowire and is/are disposed below a gate contact. Intervening layers may also be provided within the GAAFET to increase/improve electrical stability for the quantum-based features.

• Generates 4,5, or 6 states, as opposed to 2 conventional FET

• Device easily fabricated using conventional CMOS technology

• Circuit architecture very similar to CMOS binary circuits

• Device model and circuit model are compatible

• Larger, denser memory in a single transistor for greater processing power

• Increases in device integration, speed, efficiency, and cost savings

• Computer Science

• Conventional Semiconductor Manufacturing Process

• Advanced Computational Logic

• Multi-State Storage

• Large Scientific and Research Instruments

• Custom Computational Logic Devices

Patented,

US 11,799,035

Stage of Development Technology Readiness Level (TRL): 2

This technoloy is available for licensing

Licensing, Development partner