Manufacturing Method for Ultra-high Solid State Capacitance Capacitors

Fabricating the dielectric of capacitors with a thin and continuous coating, providing the best trade-off of capacitance and breakdown voltage

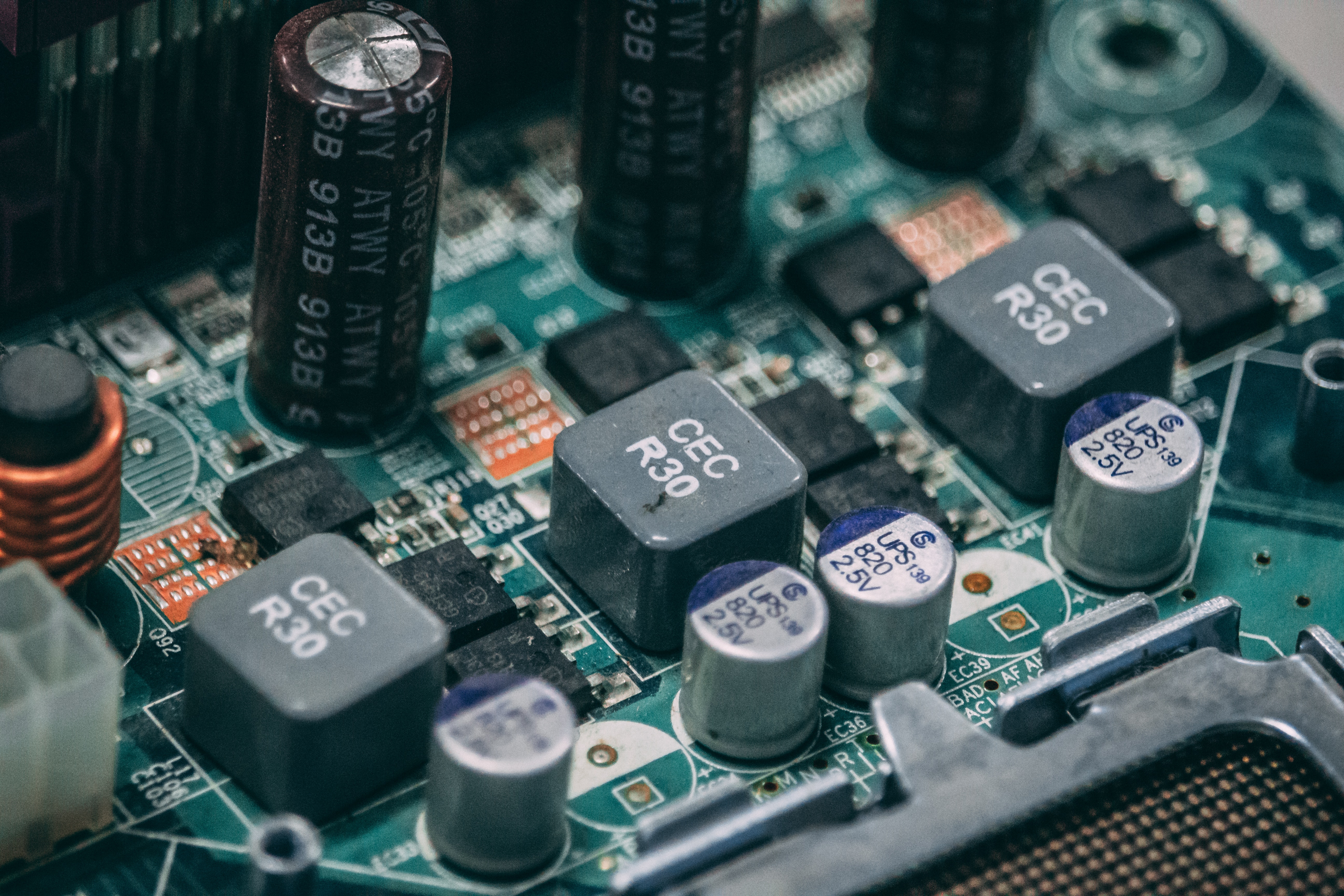

Supercapacitors are devices with high power density, moderate energy density, and long, stable life. These properties position these devices to replace or complement batteries to store and deliver electrical energy for use in electrical circuits. Supercapacitors can also serve as discrete components in electronic circuits of all types because of their small footprint. However, most supercapacitors lack sufficient energy density to work in many applications. Batteries, therefore, remain the most reliable source of stored energy.

Current capacitors require improvements, such as decreasing their environmental impact (i.e., no electrolytic fluids, or rare-earth or conflict elements), more precision, wider range of application, improved function (especially with respect to temperature and frequency), and extended lifetimes.

The capacitors developed by Binghamton University researchers have high power delivery while also having energy storage equal to or greater than some batteries.

Researchers at Binghamton University have developed a method of fabricating nanolaminate based dielectric thin film capacitors by atomic layer deposition (ALD). This method produces thin, high-purity, non-porous, defect-free dielectric layers that deliver supercapacitor like performance on smaller footprints with high specific capacitance and high breakdown voltage compared to commercial capacitors.

https://www.pexels.com/photo/black-and-white-audio-mixer-4584612/

https://www.pexels.com/photo/black-and-white-audio-mixer-4584612/

- ALD creates very thin individual layers that minimize the thickness of the stacked units to maximize specific capacitance.

- Comparable energy at significant weight advantages over conventional batteries.

- Reduced environmental impact due to the lack of electrolytic chemicals, rare earth elements or conflict materials such as tantalum.

- Use of uniform template that vastly increases the capacitor’s surface area reduces overall cost.

- Solar Cells

- Electric Vehicles

- Rapid charge devices

- Energy harvesting

- Powerhouses

- Electronic devices (phones, computers)

- Medical, and wearable devices

Patent Information:

| App Type |

Country |

Serial No. |

Patent No. |

Patent Status |

File Date |

Issued Date |

Expire Date |

|